Архитектура отладки MIPI - MIPI Debug Architecture

Эта статья слишком полагается на Рекомендации к основные источники. (Декабрь 2018 г.) (Узнайте, как и когда удалить этот шаблон сообщения) |

Архитектура отладки Альянса MIPI предоставляет стандартизированную инфраструктуру для отладка глубоко встроенные системы в мобильном и подвижном пространстве. В MIPI Альянс Рабочая группа MIPI Debug выпустила портфель спецификаций; их цель - предоставить стандартные протоколы отладки и стандартные интерфейсы из система на чипе (SoC) в инструмент отладки. Технический документ Обзор архитектуры для отладки обобщает все усилия. В последние годы группа сосредоточилась на определении протоколов, улучшающих видимость внутренних операций глубоко встраиваемых систем, стандартизации решений отладки через функциональные интерфейсы фактор формы устройств и указав использование I3C как отладочная шина.[1][2]

Термин «отладка»

Термин «отладка» охватывает различные методы, используемые для обнаружения, сортировки, отслеживания и потенциального устранения ошибок или ошибок в аппаратном и программном обеспечении. Отладка включает в себя методы управления / настройки, отладку в режиме остановки / пошагового режима и различные формы отслеживание.

Методы управления / настройки

Отладку можно использовать для управления и настройки компонентов, включая встроенные системы, данной целевой системы. Стандартные функции включают настройку оборудования контрольные точки, подготовка и настройка системы трассировки и проверка системы состояния.

Отладка в режиме остановки / пошагового режима

В режиме остановки / пошаговой отладки ядро / микроконтроллер останавливается с помощью точек останова, а затем выполняется «пошагово» по коду, выполняя инструкции по одной за раз. Если другие ядра / микроконтроллеры SoC завершили работу синхронно, можно проверить общее состояние системы. Отладка в режиме остановки / шага включает в себя методы управления / настройки, управление запуском ядра / микроконтроллера, синхронизацию запуска / остановки с другими ядрами, доступ к памяти и регистрам, а также дополнительные функции отладки, такие как счетчик производительности и доступ к памяти во время выполнения.

Отслеживание

Трассировки позволяют проводить глубокий анализ поведения и временных характеристик встроенной системы. Типичны следующие следы:

- «Базовая трассировка» обеспечивает полную видимость выполнения программы на встроенном ядре. Данные трассировки создаются для последовательности выполнения инструкций (иногда называемой трассировкой команд) и передач данных (иногда называемых трассировкой данных). SoC может генерировать несколько основных трасс.

- «Трассировка шины» обеспечивает полную видимость передачи данных по определенной шине.

- «Системная трассировка» обеспечивает видимость различных событий / состояний внутри встроенной системы. Данные трассировки могут быть сгенерированы программным кодом прибора и аппаратными модулями в SoC. SoC может генерировать несколько системных трассировок.

Видимость внутренних операций SoC

Трассировка - это предпочтительный инструмент для мониторинга и анализа того, что происходит в сложной SoC. Для рынка встраиваемых систем существует несколько хорошо зарекомендовавших себя стандартов трассировки ядра и шины, не относящихся к MIPI. Таким образом, Рабочей группе MIPI Debug не нужно было указывать новые. Но не существовало стандарта для «системной трассировки», когда Рабочая группа по отладке опубликовала свою первую версию Протокол системной трассировки MIPI (МИПИ НТП) в 2006 году.

Трассировка системного программного обеспечения MIPI (MIPI SyS-T)

Генерация данных трассировки системы из программного обеспечения обычно выполняется путем вставки дополнительных вызовов функций, которые производят диагностическую информацию, ценную для процесса отладки. Этот метод отладки называется инструментарием. Примеры: функции генерации строк в стиле printf, информация о значениях, утверждения и т. Д. Трассировка системного программного обеспечения MIPI (MIPI SyS-T) предназначен для определения многоразового универсального протокола передачи данных и инструментов API для отладки. В спецификации определены форматы сообщений, которые позволяют инструменту анализа трассировки декодировать сообщения отладки либо в удобочитаемый текст, либо в сигналы, оптимизированные для автоматического анализа.

Поскольку подробные текстовые сообщения ограничивают пропускную способность для отладки, предусмотрены так называемые «сообщения каталога». Сообщения каталога - это компактные двоичные сообщения, которые заменяют строки числовыми значениями. Преобразование числового значения в строку сообщения выполняется инструментом анализа трассировки с помощью дополнительных средств. XML Информация. Эта информация предоставляется в процессе сборки программного обеспечения с использованием схемы XML, которая также является частью спецификации.

Протокол данных SyS-T разработан для эффективной работы поверх транспортных каналов нижнего уровня, таких как те, которые определены Протокол системной трассировки MIPI. Функции протокола SyS-T, такие как отметка времени или контрольные суммы данных, могут быть отключены, если транспортный канал уже предоставляет такие возможности. Использование других транспортных связей, таких как UART, USB, или же TCP / IP - тоже возможно.

Рабочая группа по отладке MIPI предоставит эталонную реализацию с открытым исходным кодом для инструментария SyS-T API, симпатичный принтер сообщений SyS-T и инструмент для генерации дополнительных данных XML, как только Спецификация трассировки системного программного обеспечения (SyS-T) одобрен.[3]

Протокол системной трассировки MIPI (MIPI STP)

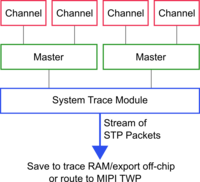

В Протокол системной трассировки MIPI (MIPI STP) определяет общий протокол, который позволяет объединять потоки трассировки, исходящие из любого места SoC, с потоком трассировки 4-битных кадров. Он был специально разработан для объединения информации трассировки системы. В Протокол системной трассировки MIPI использует топологию канал / главный, которая позволяет инструменту анализа приема трассировки сопоставлять отдельные потоки трассировки для анализа и отображения. Протокол дополнительно предоставляет следующие функции: синхронизацию и выравнивание потоков, маркеры триггеров, глобальную метку времени и синхронизацию времени нескольких потоков.

Поток пакетов STP, созданный модулем системной трассировки, может быть напрямую сохранен в ОЗУ трассировки, напрямую экспортирован за пределы кристалла или может быть направлен в модуль «протокол оболочки трассировки» (TWP) для слияния с другими потоками трассировки. РУКА Macrocell CoreSight System Trace,[4] который совместим с MIPI STP, сегодня является неотъемлемой частью большинства многоядерных чипов, используемых в мобильном пространстве.

Последняя версия, принятая MIPI Board Спецификация протокола системной трассировки (STPSM) - это версия 2.2 (февраль 2016 г.).[5]

Протокол MIPI Trace Wrapper (MIPI TWP)

В Протокол MIPI Trace Wrapper позволяет объединить несколько потоков трассировки в один поток трассировки (байтовые потоки). Каждому потоку трассировки протоколом упаковки присваивается уникальный идентификатор. Обнаружение границ байта / слова возможно, даже если данные передаются в виде потока битов. Инертные пакеты используются, если требуется непрерывный экспорт данных трассировки. Протокол MIPI Trace Wrapper основан на ARM Протокол форматирования трассировки указано для ARM CoreSight.

Последняя версия, принятая MIPI Board Спецификация протокола Trace Wrapper (TWPSM) - версия 1.1 (декабрь 2014 г.).[6]

От специализированных интерфейсов к функциональным

Выделенные интерфейсы отладки

На ранних этапах разработки продукта обычно используются платы разработки со специальными и легкодоступными интерфейсами отладки для подключения инструментов отладки. SoC, используемые на рынке мобильных устройств, основаны на двух технологиях отладки: отладка в режиме остановки с помощью цепочки сканирования и отладка в режиме остановки с помощью регистров отладки с отображением в память.

Следующие стандарты отладки, не относящиеся к MIPI, хорошо зарекомендовали себя на рынке встраиваемых систем: IEEE 1149.1 (5-контактный) и ARM Serial Wire Debug (2-контактный), оба используют несимметричные контакты. Таким образом, рабочей группе MIPI Debug не было необходимости указывать протокол отладки в режиме остановки или указывать интерфейс отладки.

Данные трассировки, сгенерированные и объединенные в поток трассировки в SoC, могут быть переданы через выделенный однонаправленный интерфейс трассировки вне кристалла в инструмент анализа трассировки. Архитектура отладки MIPI предоставляет спецификации как для параллельных, так и для последовательных портов трассировки.

В Интерфейс параллельной трассировки MIPI (MIPI PTI) определяет, как передавать данные трассировки на несколько выводов данных и вывод синхронизации (несимметричный). Спецификация включает имена сигналов и функции, временные характеристики и электрические ограничения. Последняя версия, принятая MIPI Board Спецификация интерфейса параллельной трассировки это версия 2.0 (октябрь 2011 г.).[7]

В Интерфейс высокоскоростной трассировки MIPI (MIPI HTI) определяет, как передавать данные трассировки через физический уровень стандартных интерфейсов, например PCI Express, DisplayPort, HDMI, или USB. Текущая версия спецификации позволяет использовать от одной до шести полос. В спецификацию входят:

- Уровень PHY, который представляет электрические и тактовые характеристики последовательных линий.

- Слой LINK, который определяет, как трасса упаковывается в Aurora. 8B / 10B протокол.

- Модель программиста для управления HTI и предоставления информации о состоянии.

HTI - это подмножество Высокоскоростной последовательный порт трассировки (HSSTP) спецификация, определенная ARM.[8] Последняя версия, принятая MIPI Board Спецификация высокоскоростного интерфейса трассировки это версия 1.0 (июль 2016 г.).[9]

Разработчики плат и поставщики средств отладки извлекают выгоду из стандартных разъемов отладки и стандартного назначения контактов. В Рекомендации MIPI для соединителей отладки и трассировки рекомендует 10- / 20- / 34-контактные разъемы 1,27 мм (0,050 дюйма) на уровне платы (MIPI10 / 20/34). Было указано семь различных назначений контактов, которые предназначены для самых разных сценариев отладки. Они включают в себя стандартный JTAG (IEEE 1149.1), cJTAG (IEEE 1149.7) и 4-битные параллельные интерфейсы трассировки (в основном используемые для системных трассировок), дополненные стандартом Serial Wire Debug (SWD) для ARM.[10] Отладочные разъемы MIPI10 / 20/34 стали стандартом для встраиваемых систем на базе ARM.

Многие встраиваемые конструкции в мобильном пространстве используют высокоскоростные параллельные порты трассировки (до 600 мегабит в секунду на контакт). MIPI рекомендует 60-контактный разъем Samtec QSH / QTH с именем MIPI60, который позволяет JTAG / cJTAG для управления запуском, до 40 сигналов данных трассировки и до 4 тактовых импульсов трассировки. Чтобы минимизировать сложность, в рекомендации определены четыре стандартные конфигурации с одним, двумя, тремя или четырьмя каналами трассировки различной ширины.

Последняя версия, принятая MIPI Board Рекомендации альянса MIPI для соединителей отладки и трассировки это версия 1.1 (март 2011 г.).[11]

PHY и контактные интерфейсы с наложением

Легкодоступные интерфейсы отладки недоступны в окончательном форм-факторе продукта. Это затрудняет выявление ошибок и оптимизацию производительности в конечном продукте. Поскольку логика отладки все еще присутствует в конечном продукте, необходим альтернативный путь доступа. Эффективный способ - оснастить стандартный интерфейс мобильного терминала мультиплексором, который позволяет получить доступ к логике отладки. Переключение между основной функцией интерфейса и функцией отладки может быть инициировано подключенным инструментом отладки или программным обеспечением мобильного терминала. Стандартные средства отладки можно использовать при следующих условиях:

- Протокол переключения реализован в инструменте отладки и в мобильном терминале.

- Существует адаптер отладки, который соединяет инструмент отладки со стандартным интерфейсом. Адаптер отладки должен при необходимости поддерживать протокол переключения.

- Указывается отображение стандартных контактов интерфейса на контакты отладки.

В Узкий интерфейс MIPI для отладки и тестирования (MIPI NIDnT) охватывает отладку через следующие стандартные интерфейсы:microSD, Разъем USB 2.0 Micro-B / -AB, разъем USB Type-C и порт DisplayPort. Последняя версия, принятая MIPI Board Спецификация узкого интерфейса для отладки и тестирования (NIDnTSM) - версия 1.2 (декабрь 2017 г.).[12]

Сетевые интерфейсы

Вместо повторного использования контактов отладку можно также выполнять через стек протоколов стандартного интерфейса или сети. Здесь отладочный трафик сосуществует с трафиком других приложений, использующих тот же канал связи. Рабочая группа MIPI Debug назвала этот подход GigaBit Debug. Поскольку для этого подхода не существовало протокола отладки, рабочая группа отладки MIPI указала свой протокол отладки SneakPeak.

Протокол MIPI SneakPeek (MIPI SPP) перешел с выделенного интерфейса для базовой отладки на интерфейс, управляемый протоколом:

- Он преобразует входящие пакеты команд в доступ для чтения / записи к памяти, отображенным в память регистрам отладки и другим отображенным в память системным ресурсам.

- Он преобразует результаты команд (информацию о состоянии и считанные данные, поступающие из памяти, отображенные в память регистры отладки и другие отображенные в память системные ресурсы) в исходящие ответные пакеты.

- Поскольку SneakPeek принимает пакеты, проходящие через входной буфер, и доставляет пакеты через выходной буфер, его можно легко подключить к любому стандартному вводу-выводу или сети.

В Спецификация MIPI Alliance для протокола SneakPeek описывает основные концепции, необходимую инфраструктуру, пакеты и поток данных. Последняя версия, принятая MIPI Board Спецификация протокола SneakPeek (SPPSM) - версия 1.0 (август 2015 г.).[13]

В Семейство спецификаций отладки MIPI Gigabit Debug предоставляет подробные сведения для сопоставления протоколов отладки и трассировки со стандартными операциями ввода-вывода или сетями, доступными в мобильных терминалах. Эти сведения включают в себя: адресацию конечных точек, инициализацию каналов и управление ими, упаковку данных, управление потоками данных, а также обнаружение и восстановление ошибок. Последняя версия, принятая MIPI Board Спецификация Gigabit Debug для USB (MIPI GbD USB) - версия 1.1 (март 2018 г.).[14] Последняя версия, принятая MIPI Board Спецификация для гигабитной отладки для сокетов интернет-протокола (MIPI GbD IPS) - версия 1.0 (июль 2016 г.).[15]

I3C как шина отладки

Текущие решения для отладки, такие как JTAG и ARM CoreSight, имеют статическую структуру, что ограничивает масштабируемость в отношении доступности компонентов / устройств отладки. Отладка MIPI для I3C определяет масштабируемое 2-контактное одностороннее решение отладки, которое имеет то преимущество, что оно доступно в течение всего срока службы продукта. Шину I3C можно использовать только как шину отладки, или шину можно использовать совместно между отладкой и ее основной функцией в качестве шины сбора данных для датчиков. Отладка через I3C в принципе работает следующим образом:

- Шина I3C используется для физического транспорта, а встроенные функции I3C используются для настройки шины и горячего соединения новых компонентов.

- Протокол отладки заключен в специальные команды I3C. Поддерживаемые протоколы отладки: JTAG, ARM CoreSight и протокол MIPI SneakPeek.[13]

Рекомендации

- ^ «Рабочая группа по отладке». MIPI Альянс. 2019. Получено 7 июн 2019.

- ^ «Обзор архитектуры для отладки» (PDF). MIPI Альянс. Версия 1.2. 13 июля 2018 г.. Получено 7 июн 2019.

- ^ «Системное программное обеспечение MIPI - Trace (MIPI SyS-T)». MIPI Альянс. Версия 1.0. Апрель 2018 г.. Получено 7 июн 2019.

- ^ "Макроячейка трассировки системы". ARM Разработчик. 2019. Получено 7 июн 2019.

- ^ «Протокол трассировки системы MIPI (MIPI STP)». MIPI Альянс. Версия 2.2. Февраль 2016 г.. Получено 7 июн 2019.

- ^ «Протокол MIPI Trace Wrapper (MIPI TWP)». MIPI Альянс. Версия 1.1. Декабрь 2014 г.. Получено 7 июн 2019.

- ^ «Интерфейс параллельной трассировки MIPI (MIPI PTI)». MIPI Альянс. Версия 2.0. Октябрь 2011 г.. Получено 8 июн 2019.

- ^ «Обзор архитектуры CoreSight: порт высокоскоростной последовательной трассировки (HSSPT)». ARM Разработчик. 2019. Получено 8 июн 2019.

- ^ «Интерфейс высокоскоростной трассировки MIPI (MIPI HTI)». MIPI Альянс. Версия 1.0. Июль 2016. Получено 8 июн 2019.

- ^ «Отладка последовательного кабеля». ARM Разработчик. 2019. Получено 8 июн 2019.

- ^ «Рекомендации Альянса MIPI для соединителей отладки и трассировки». MIPI Альянс.

- ^ «Узкий интерфейс MIPI для отладки и тестирования (MIPI NIDnT)». MIPI Альянс. Версия 1.2. Декабрь 2017 г.. Получено 9 июн 2019.

- ^ а б «Протокол MIPI SneakPeek (MIPI SPP)». MIPI Альянс. Версия 1.0. Август 2015 г.. Получено 9 июн 2019.

- ^ «MIPI Gigabit Debug для USB (MIPI GbD USB)». MIPI Альянс. Версия 1.1. Март 2018 г.. Получено 9 июн 2019.

- ^ «MIPI Gigabit Debug для IP-сокетов (MIPI GbD IPS)». MIPI Альянс. Версия 1.0. Июль 2016. Получено 9 июн 2019.

внешняя ссылка

- Шульц, Норберт (Intel Corporation) (26 сентября 2016 г.). Как спецификации отладки MIPI помогают мне в разработке системного ПО. MIPI DevCon 2016. Получено 9 июн 2019.